# DESIGN OF CNTFET BASED SYNCHRONOUS UP COUNTER FOR ULTRA LOW POWER APPLICATIONS

Saravanan V.<sup>1</sup> Kannan V.<sup>2</sup>

<sup>1</sup> Research Scholar, Sathyabama University, Tamilnadu, India <sup>2</sup>Jeppiaar Institute of Technology, Tamilnadu, India.

#### Abstract

This paper presents the ultra low power synchronous counter using carbon nanotube Field Effect Transistor. The proposed counter is designed using 18 nm technology. The counter is designed using T flip flop. Proposed design minimizes the power consumption and operating voltage. As far as it is known, this is the first attempt to design synchronous counter using CNTFET. Results of the design are compared with CMOS technology based synchronous counter. This paper also presents design and simulation of T flip flop.

Keywords: Synchronous counter, Ultra low power, CNTFET, Power Consumption, CMOS.

#### I. INTRODUCTION

A synchronous counter is a sequential circuit that produces a specified count sequence. The count changes whenever the input clock is asserted. It is a one of the essential building blocks in very large scale integration design. In many applications such as microprocessors, memories, communication devices, ultra low power digital circuits, nano devices, wireless communication etc. designing low power synchronous counter is highly desirable. CMOS technology is the mainstream technology used in the last few decades for designing of many digital circuits. The last few decades metal oxide semiconductor field effect transistor (MOSFET) size has continually been reduced in CMOS technology, this reduction; increase the no of transistor on chip and cost of the chip, chip with more functionality in the same area. Designing MOSFETs with channel lengths much smaller than a micrometre is a challenge, and creates the problems in device fabrication, which limits advancing the integrated circuit, Small size of the MOSFET, below a tens of nanometres creates the low oxide Trans-conductance. gate leakage, low ON-current, Mobility degradation, increased delay.

The operation of conventional synchronous counters is very inefficient as far as the switching power consumption is concerned, due to lot of redundant transitions on internal switching nodes during counting operations. The operation of conventional synchronous counters is usually based on a synchronous timing principle in which new data values of the entire counter bits are evaluated at every clock

cycle and captured by associated flip-flops (FFs) at every triggering edge of the clock. Because the switching activity of counter bits in a binary counter is decreased by half for each bit increase. This type of operation apparently causes a lot of redundant transitions.

In the Asynchronous binary counter the output of one counter stage is connected directly to the clock input of the next counter stage and so on along the chain, and as a result the asynchronous counter suffers Propagation Delay, However with Synchronous Counter, the external clock signal is connected to the clock input of all flip-flop within the counter so that all of the flip-flops are clocked together simultaneously at the same time giving a fixed time relationship. This results in all the individual output bits changing state at exactly the same time in response to the common clock signal with no ripple effect and therefore, no propagation delay. When the synchronous counters are designed for very high speed and low power digital circuits in the nano metre ranges, CMOS technology has started to face the many difficult challenges. In this paper CNTFET is introduced for designing synchronous counter in the 18nm scale range. since in CNTFET, carbon nanotube is used as channel and high-k material is used as gate dielectric problems observed in the MOSFET when size is reduced are avoided. Synchronous counters are easier to design. Overall faster operation may be achieved compared to Asynchronous counters.

The rest of this paper is organized as follows: Section II describes the carbon nanotube field effect transistors. Session III describes CNTFET Theory, Session IV describes the HSPICE model of CNTFET. Session V narrates the design of T flip flop and synchronous up counter using CNTFET. Session VI provide the simulation results and discussion. Session VII provides conclusion.

## **II. CARBON NANOTUBES**

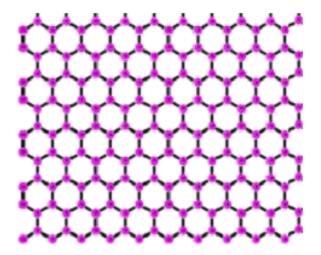

Carbon nanotubes (CNTs) are hollow cylinders, which is composed of one or more concentric layers of carbon atoms. Carbon nanotubes (CNT) have significant physical and chemical properties. CNTs, only 1-2 nm in diameter, have a tensile strength that is 375 times greater than that of steel. In addition, the Young's modulus and thermal conductivity of CNTs are nearly those of diamond. The density of a hexagonal array of CNTs is about 1.4 g/cm<sup>3</sup>. This combination of properties leads to a wide variety of potential applications. Single-walled carbon nanotubes (SWCNT) are attractive for extreme scaling of integrated circuits due to their small diameters (~ 1 nm) long lengths ( $\sim$  100  $\mu$  m) and thermal stabilities. A SWCNT can be either semi-conducting or metallic, and electrical properties depends on the tube's longitudinal axis relative to principal axes of a graphene sheet (helicity) and its diameter. SWCNTs are being considered for application as transistors, diodes, and interconnects in future integrated circuits.

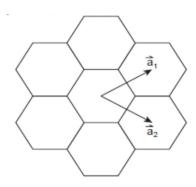

CNTs properties are strongly dependent on their chirality and diameter. The chirality is related to the degree of the twist of the lattice of the tube and can be described by the chiral vector. The chiral vector is a circular vector that is perpendicular to the axis of the tube. It is a linear combination of the base vectors  $\mathbf{a}_1$  and  $\mathbf{a}_2$ . In mathematical terms the chiral vector is defined by equation (1):

$$C = na_1 + ma_2$$

...(1)

Where n and m are integers.

Graphical representation of the chiral vector is shown in fig (2)

Carbon nanotube field effect transistors (CNTFETs) utilize semi conducting single wall CNTs to assemble electronic devices.

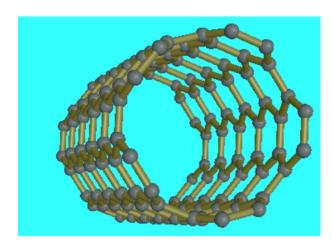

A single-wall carbon nanotube (SWCNT) consists of one cylinder only as shown in fig (3) and the

Fig. 1. Structure of graphene

Fig. 2. Chiral vector

Fig. 3. single-wall carbon nanotube

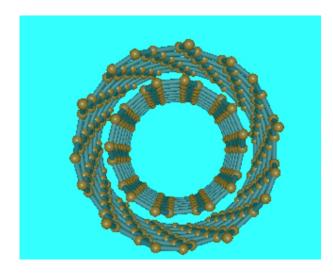

Multi-wall carbon nanotube (MWCNT) consists of more than one CNT as in fig (4). Simple manufacturing process of this device makes it very promising replacement of MOSFET Technology. The density of

Fig. 4. Multi-wall carbon nanotube

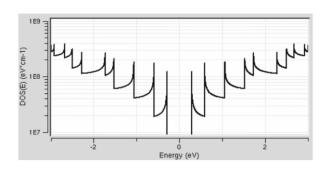

states (DOS) of the carbon nanotube can be obtained by using the equation (2).

$$g(E) = \frac{2}{\pi} \sum_{m} \int \left| \frac{\partial E_{CNT}}{\partial K_{t}} \right|^{1} dE_{CNT} \qquad \dots (2)$$

$\mathsf{E}_{\mathsf{CNT}}$  is the the dispersion of CNT, m is quantization number in the circumferential direction. The density of states of CNT is shown in fig (4)

Fig. 5. DOS of (19, 0) Nano tube

## III. CNTFET THEORY

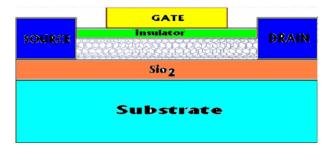

Carbon nanotube field effect transistor (CNTFET) are currently considered one of the main building block for the replacement of MOSFET based CMOS technology. The core of a CNTFET is carbon nanotube. Similar to the MOSFET device, the CNTFET has also four terminals. The current-voltage (I-V) characteristics of the CNTFET are similar to MOSFET's.

Fig (6) Schematic diagram of a carbon nanotube transistor

Fig. 6.

The diameter of the CNT can be calculated based on the following equation (3).

$$D_{CNT} = \frac{a\sqrt{n_1^2 + n_1 n_2 + n_2^2}}{\pi} \qquad ...(3)$$

The threshold voltage is defined as the voltage required to turn ON transistor. The threshold voltage of the intrinsic CNT channel can be approximated to the first order, as the half band gap is an inverse function of the diameter and the equation for threshold voltage is defined by (4).

$$V_{th} \approx \frac{Eg}{2e} = \frac{\sqrt{3}}{3} \frac{aV\pi}{e D CNT} \qquad \dots (4)$$

where a=2.49 Å is the carbon to carbon atom distance, V=3.033 eV is the carbon - bond energy in the tight bonding model, e is the unit electron charge, and  $_{CNT}$  is the CNT diameter. D CNT of a (19, 0) CNT is 1.487 nm, the threshold voltage of a CNTFET using (19, 0) CNTs as channels, is 0.293V, The device channel consists of a (19, 0), zigzag CNT with a band gap of 0.53 eV and a diameter of 1.5 nm.

## IV. HSPICE MODEL OF CNTFET

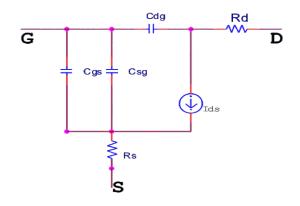

Fig (6) shows the schematic of MOSFET like CNTFET used for designing the reversible gates and adder circuits. It's HSPICE model is shown in fig (7), model consists of two main parts, current sources and capacitance networks. For semi conducting sub-bands electron current is only considered for the nFET, because the hole current is suppressed by the n-type heavily doped source, drain, and usually is negligible compared to the electron current. The current contributed by the semi conducting sub-bands is given by equation (5)

$$I_{D} = 2\sum_{km}^{M} \sum_{ki}^{L} \left[ J_{m.l}(0, \Delta \Phi_{B}) - J_{m.l}(V_{ck.DS}, \Delta \Phi_{3}) \right]$$

...(5)

J  $_{m,l}$  () is the current contributed by the substate (m,l). Various capacitaces used in model are calculated by equation, (6), (7), (8), (9), (10).

$$C_{sg} = \frac{L_g}{2} \left( C_{as} - \frac{1}{e} \frac{C_{tot} - 2(1 - \beta) C_2}{\partial V_G / \partial \Delta \Phi_B} \right) \qquad \dots (6)$$

Fig. 7. HSPICE model of CNTFET

$$C_{dg} = \frac{L_g}{2} \left( C_{as} - \frac{1}{e} \frac{C_{tot} - 2 \beta C_c}{e \partial V_G \partial \Delta \Phi_B} \right) \qquad \dots (7)$$

$$C_{Qs} = \frac{4e^2}{L_g \cdot KT} \sum_{k_m}^{M} \sum_{k_i}^{L} \left[ \frac{e^{E_{mj} - \Delta \Phi_g)/KT}}{(1 + e^{(E_{mj} - \Delta \Phi_g)/KT})^2} \right] \qquad ...(8)$$

$$C_{Qd} = \frac{4e^2}{L_g \cdot KT} \sum_{k_m}^{M} \sum_{k_i}^{L} \left[ \frac{e^{(E_{mJ} - \Delta \Phi_B + eV_{ch \cdot DK})/KT \dots (9)}}{(1 + e^{(E_{mJ} - \Delta \Phi_B + eV_{ch \cdot DR})/KT})^2} \right]$$

$$C_{p} = \frac{L_{g} C_{ax} [C_{p} + (1 - \beta) C_{c}}{C_{tot} C_{Qs} + C_{Qd}} \qquad ...(10)$$

## V. DESIGN OF CNTFET BASED T-FLIP FLOP AND SYNCHRONOUS COUNTER

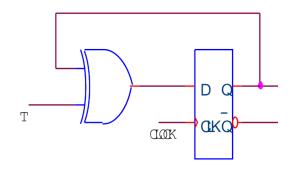

Flip-flops can be used to form registers capable of holding or manipulating multiple bits of data ,This session presents the carbon nanotube field effect transistor based T Flip Flop using D Flip Flop, Here both PCNTFET and NCNTFET are used to design the D Flip Flop and T Flip Flop. Both the type of CNTFET are modelled using same diameter of CNTs, length of the CNT is 18nm, threshold voltage of device is 0.293 v ,chirality of CNT is (19,0). Fig 8 shows the T Flip Flop circuit. Also Table 1 shows the truth table of T Flip Flop.

Fig. 8. CNTFET based T Flip Flop circuit

Table 1. T- Flip Flop Truth Table

| Т | CLOCK | Qa        | <b>Q</b> b |

|---|-------|-----------|------------|

| 0 | 0     | No change | No change  |

| 1 | 1     | TOGGLE    | TOGGLE     |

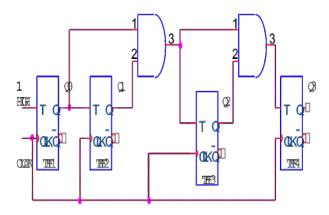

In synchronous counters, the clock inputs of all the flip-flops are connected together and are triggered by the input pulses. Hence all the flip-flops state changes simultaneously. Fig. 9. shows the 4-bit synchronous counter circuit. The T input of FF1 is connected to HIGH. FF2 input (T) is connected to the output of FF1, and the T input of FF3 is connected to the output of an AND gate that is fed by the outputs of FF1 and FF2 and so on. Table 2 shows the counting sequence of the 4 bit synchronous counter.

Fig. 9. CNTFET Based Synchronous Counter

Table 2. Counting sequence of synchronous counter

| Clock<br>Pulse | <i>Q</i> <sub>3</sub> | Q <sub>2</sub> | Q <sub>1</sub> | $Q_0$ |

|----------------|-----------------------|----------------|----------------|-------|

| Initially      | 0                     | 0              | 0              | 0     |

| 1              | 0                     | 0              | 0              | 1     |

| 2              | 0                     | 0              | 1              | 0     |

| 3              | 0                     | 0              | 1              | 1     |

| 4              | 0                     | 1              | 0              | 0     |

| 5              | 0                     | 1              | 0              | 1     |

| 6              | 0                     | 1              | 1              | 0     |

| 7              | 0                     | 1              | 1              | 1     |

| 8              | 1                     | 0              | 0              | 0     |

| 9              | 1                     | 0              | 0              | 1     |

| 10             | 1                     | 0              | 1              | 0     |

| 11             | 1                     | 0              | 1              | 1     |

| 12             | 1                     | 1              | 0              | 0     |

| 13             | 1                     | 1              | 0              | 1     |

| 14             | 1                     | 1              | 1              | 0     |

| 15             | 1                     | 1              | 1              | 1     |

| 16             | 0                     | 0              | 0              | 0     |

#### VI. SIMULATION RESULTS AND DISCUSSION

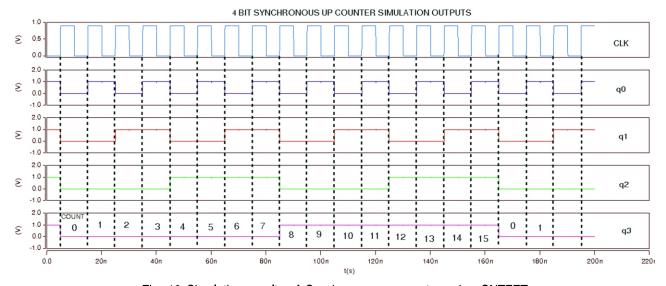

In the proposed design, CNTFET is used for designing 4 bit synchronous counter. Fig 10 shows the

Simulation results of the 4 bit counter, the propagation delay  $t_{PLH}$  of 4 bit CNTFET based counter is 4.9 ps where as for CMOS based design 5.12 ns. Similarly propagation delay of  $t_{PHL}$  for CNTFET based design is 10.6 ps and for CMOS based design 39.9 ps. This less propagation delay of CNTFET based design gives total delay of the 4 bit counter is 7.75 ps where as in CMOS 2.54 ns. Power consumption of the 4 bit CNTFET counter is 0.15  $\mu$  W and for CMOS counter is 1.08  $\mu$  W. Simulated parameters of 4 bit counter is shown in Table 3. From the Simulated results of CNTFET based counter it provides high speed of counting with low power consumption and low operating voltage. The proposed counters can be used for modern frequency synthesizer, phased locked loop, etc.,

Table 3. Simulated parameters of 4 bit counter

| PARAMETERS                      | 4 Bit Counter |         |  |

|---------------------------------|---------------|---------|--|

|                                 | CMOS          | CNTFET  |  |

| Channel length (mm)             | 180           | 18      |  |

| Supply Voltage                  | 1v            | 0.9V    |  |

| t <sub>PLH</sub>                | 5.12 ns       | 4.9 PS  |  |

| t <sub>PHL</sub>                | 39.9 Ps       | 10.6 PS |  |

| Average Power (μw)              | 1.08          | 0.156   |  |

| Delay(s)                        | 2.54 n        | 7.75 ps |  |

| Power Delay Product<br>(Joules) | 2.74 fJ       | 1.2 aJ  |  |

Fig. 10 Simulation results of Synchronous up counter using CNTFET

## VII. CONCLUSION

This paper describes the design of 4 bit synchronous up counter and T flip flop using carbon nanotube field effect transistor. Simulation is done for both CMOS and CNTFET based technology. CNTFET based design is simulated in 18nm technological node and CMOS based design is simulated in 180nm technological node CNTFET has been proposed in this paper to achieve high-speed operation with low power. Hence CNTFET based counter design will be best replacement for CMOS based design in ultra low power applications.

### **REFERENCES**

- [1] Appenzeller J (2008), "Carbon Nanotubes for High-Performance Electronics Progress and Prospect", *Proceedings of the IEEE*, Vol.96, No.2, pp.201-211.

- [2] Appenzeller J, Radosavljevic M, Knoch J and Avouris Ph. (2004), "Tunneling Versus Thermionic Emission in One Dimensional/Semiconductors", *Physical Review Letters*, Vol.92, No.4.

- [3] Appenzeller J, Yu-Ming Lin, Knoch J *et al.* (2005), "Comparing Carbon Nanotube Transistors The Ideal Choice: A Novel Tunnelling Device Design", *IEEE Trans. Elec. Dev.*, Vol.52.

- [4] Bachtold A, Hadley P, Nakanishi T and Dekker (2001), "Logic Circuits with Carbon Nanotube Transistors", *Science*, Vol.294, No.9, pp.1317-1320.

- [5] Chen Z, Appenzeller J, Lin Y-M et al. (2006), "An Integrated Logic Circuit Assembled on a Single Carbon Nanotube", Science, Vol.311, No.5768, p.1735.

- [6] Han J and Jonker P (2002), "A System Architecture Solution for Unreliable Nanoelectronic Devices", *IEEE Trans. Nanotechnology*, Vol.1, No.4, pp.201-208.

- [7] Heinze S *et al.* (2002), "Carbon Nanotubes as Schottky Barrier Transistors", *Physical Review Letters*, Vol. 89.

- [8] Li J, Zhang Q, Yan Y et al. (2007), "Fabrication of Carbon Nanotube Field-Effect Transistors by Fluidic Alignment Technique", IEEE Transactions on Nano-Technology, Vol.6, No.4, pp.481-484.

- [9] Mintmire J W and White C T (1998), "Universal Density of States for Carbon Nanotubes", *Physical Review Letters*, Vol.81, pp.2506-2509.

- [10] Pecchia A *et al.* (2003), "Electronic Transport Properties of Molecular Devices", *Physical Review Letters, Vol.19, Nos 1&2, pp.139-144.*

- [11] Postma H, Teepen T, Yao Z *et al.* (2001), "Carbon Nanotube Single-Electron Transistors at Room Temperature", *Science*, Vol.293, No.5527, pp.76-79.

- [12] Radosavljevic M *et al.* (2003), "Drain Voltage Scaling in Carbon Nanotube Transistors", *Appl. Phys. Lett.*, Vol.83, No.12, p.2435-2437.

- [13] Rahman A, Jing Guo, Datta S and Lundstrom M S (2003), "Theory of Ballistic Nanotransistors", IEEE Transactions on Electron Devices, Vol.50,No.10, pp.1853-1864,

- [14] Raychowdhury A and Roy K (2005), "Carbon-Nanotube-Based Voltage-Mode Multiple-Valued Logic Design", *IEEE Trans. Nanotechnology*, Vol.4, No.2, pp.168-179.

- [15] Raychowdhury A, Mukhopadhyay S and Roy K (2004), "A Circuit Compatible Model of Ballistic Carbon Nanotube FETs", IEEE Trans. on CAD, Vol.23, pp.1411-1420.

- [16] Rondoni D and Hoekstra J (2005), "Towards Models for CNT Devices", *IEEE ProRISC'05*, pp. 272-278.

- [17] Saito R, Dresselhaus G and Dresselhaus M S *Physical Properties of Carbon Nanotubes*, Imperial College Press, London.

- [18] Sheng Lin, Yong-Bin Kim and Fabrizio Lombardi (2008), "A New Sram Cell Design Using CNTFETs", Int SoC Design Conference, pp.168-171.

- [19] Sordan R, Balasubramanian K, Burghard M and Kern K (2006), "Exclusive-OR Gate with a Single Carbon Nanotube", Applied Physics Letters, Vol.88.

- Tawfik S.A, Zhiyu Liu and Kursun V (2007), Independent-Gate and Tied-Gate FinFET SRAM Circuits: Design Guidelines for Reduced Area and Enhanced Stability", International Conference on Microelectronics (ICM 2007), pp.171-174, December 29-31.

- 21. www.nanohub.org

V. Saravanan was born in Vellore, Tamil nadu, India in 1981. He received his bachelor degree in Electronics and Vommunication Engineering from Ganadhipathy Tulsi's Engineering College, Vellore, TamilNadu in the year 2004, ME in Applied Electronics from Sathyabama University,

Chennai in the year 2007. He is presently a research scholar in the Department of Electronics and communication Engineering, Sathyabama University. He has 8 years of teaching experience. He is a life member of ISTE.

**Dr. V. Kannan** was born in Ariyalore, Tamil nadu, India in 1970. He received his Bachelor Degree in Electronics and Communication Engineering from Madurai Kamarajar University in the year 1991, Masters Degree in Electronics and control from BITS, Pilani in the year 1996 and Ph.D.,

from Sathyabama University, Chennai, in the year 2006. His interested areas of research are Optoelectronic Devices, VLSI Design, Nano Electronics, Digital Signal Processing and Image Processing. He has 130 Research publications in National International Journals/Conferences to his credit. He has 20 years of experience in teaching and presently working as Principal of Jeppiaar Institute of Technology, Chennai, India, He is a life member of ISTE.